包含具有压缩应力AlGaAsP层的垂直共振腔表面放射激光二极管(VCSEL)的制作方法

as两者间晶格不匹配,结果a

x

ga

1-x as厚层材料会产生压缩应力因而变形翘曲,而厚层材料的变形问题在大面积装置中有影响组件效能的问题且使制程变得复杂;839案并提到当ingaasp厚层材料是形成在gaas基板之上时,会有许多晶格匹配的材料可供选用,且ingaasp是提供拉伸应力时,能降低因其他制程引起的应力。此篇专利还教示当al

x

ga

1-x as厚层材料是形成在gaas基板时,al

x

ga

1-x as会产生一些压缩应力,因此导致效能与制程的问题。

[0009]

839案的特点是让两种材料的晶格为匹配,也就是基板为gaas基板,而厚层材料是选用al

x

ga

1-x

as

z

p

1-z

,尤其是al

x

ga

1-x

as

z

p

1-z

的晶格常数须匹配于gaas基板的晶格常数,或al

x

ga

1-x

as

z

p

1-z

的晶格常数可小于gaas基板的晶格常数,以达成使整体结构保持在平整或在拉伸应力的状态下。

技术实现要素:

[0010]

但按照839案做出的vcsel磊芯片(epi wafer),实际上却发现vcsel磊芯片的差排(dislocation)或缺陷很多,或vcsel磊芯片的某些部分(on wafer uniformity)的差排或缺陷偏多,如此反而容易导致vcsel组件的可靠度变差。即便如839案所述,algaasp厚层结构的晶格常数能刚好匹配于gaas基板,但长晶过程中的温度远高于室温,且algaasp与gaas的材料热膨胀系数不同,因此在温度较高的环境下algaasp层会产生拉伸应力,而实际在vcsel磊晶成长过程中,algaasp层在拉伸应力状态下比在压缩应力状态下更容易引发差排或缺陷。

[0011]

在vcsel磊芯片的制程,当algaasp磊晶层实际在gaas基板上磊晶成长时,现有磊晶成长技术尚无法使磊晶层各处的材料成分完全均匀一致。当algaasp磊晶层的中心区域的晶格常数晶格匹配于gaas基板的晶格常数,algaasp磊晶层边缘部分的含磷量会较多。含磷量较多的部分因晶格常数小于gaas基板因而在室温下已具有拉伸应力,由于磊晶成长时温度远高于室温,因此algaasp磊晶层的含磷量较多的部分的拉伸应力会更大,拉伸应力越大vcsel磊芯片的差排或缺陷也越容易产生。

[0012]

对于太阳能磊芯片或崩溃光二极管(avalanche photo diode,apd),或许839案提供的方法确实有其所述的功效,但对vcsel磊芯片却会造成vcsel组件的可靠度或良率的问题,因为根据实验结果,以839案方法所制作出的vcsel磊芯片,vcsel磊芯片的全部或局部存在过多的差排或缺陷。

[0013]

本说明书提出一种包含具有压缩应力algaasp层的垂直共振腔表面放射激光二极管,包括gaas基板、下dbr层、下间隔层、主动区、上间隔层及上dbr层,下dbr层与下间隔层位于gaas基板之上且在主动区之下,上dbr层与上间隔层位于主动区之上;下dbr层及上dbr层分别包含多层的低折射率层及多层的高折射率层,其中,下dbr层、下间隔层、上间隔层或上dbr层的至少一部分包含al

x

ga

1-x

as

1-y

p

y

,且0<x≦1,其中,在室温下al

x

ga

1-x

as

1-y

p

y

的晶格常数大于gaas基板的晶格常数。

[0014]

低折射率层的al

x

ga

1-x

as

1-y

p

y

中磷的含量范围可为0<y≦0.03;高折射率层的al

x

ga

1-x

as

1-y

p

y

中磷的含量范围可为0<y≦0.015。

[0015]

在一实施例中,下dbr层为n型dbr层及上dbr层的至少一部分为p型dbr层,下dbr层及上dbr层分别包含多层的低折射率层及多层的高折射率层,其中,低折射率层及/或高折

射率层的至少一部分材料为al

x

ga

1-x

as

1-y

p

y

。或者,下dbr层为n型dbr层时,上dbr层则至少包含p型dbr层或同时包含p型dbr层与n型dbr层,下dbr层的n型dbr层的至少一部份、上dbr层的p型dbr层的至少一部份或上dbr层的n型dbr层的至少一部份的材料是al

x

ga

1-x

as

1-y

p

y

。

[0016]

在一实施例中,下dbr层及上dbr层的其中一者为n型dbr层且另一者为p型dbr层,下dbr层及上dbr层分别包含多层的低折射率层及多层的高折射率层,其中,低折射率层及/或高折射率层的至少一部分材料为al

x

ga

1-x

as

1-y

p

y

。或者,下dbr层为p型dbr层时,上dbr层则至少包含n型dbr层或同时包含n型dbr层与p型dbr层,下dbr层的p型dbr层的至少一部份、上dbr层的n型dbr层的至少一部份或上dbr层的p型dbr层的至少一部份的材料是al

x

ga

1-x

as

1-y

p

y

。

[0017]

在一实施例中,下dbr层及上dbr层的其中一者为n型dbr层且另一者为p型dbr层,材料为al

x

ga

1-x

as

1-y

p

y

的低折射率层及/或高折射率层可设置于n型dbr层。

[0018]

在一实施例中,下dbr层及上dbr层的其中一者为n型dbr层且另一者为p型dbr层,材料为al

x

ga

1-x

as

1-y

p

y

的低折射率层及/或高折射率层可设置于p型dbr层。

[0019]

在一实施例中,下dbr层及上dbr层的其中一者为n型dbr层且另一者为p型dbr层,材料为al

x

ga

1-x

as

1-y

p

y

的低折射率层及/或高折射率层可设置于n型dbr层与p型dbr层。

[0020]

在一实施例中,低折射率层及高折射率层材料皆为al

x

ga

1-x

as

1-y

p

y

。

[0021]

在一实施例中,在材料为al

x

ga

1-x

as

1-y

p

y

的低折射率层中,其中,0.7≦x≦1。

[0022]

在一实施例中,在材料为al

x

ga

1-x

as

1-y

p

y

的高折射率层中,其中,0<x≦0.5。

[0023]

在一实施例中,材料为al

x

ga

1-x

as

1-y

p

y

的低折射率层及/或高折射率层为材料均匀区。

[0024]

在一实施例中,材料为al

x

ga

1-x

as

1-y

p

y

的低折射率层及/或高折射率层为材料非均匀区。

[0025]

在一实施例中,更包含能隙渐变层,能隙渐变层设置于一对的低折射率层及高折射率层之间,其中,能隙渐变层的能隙会有变化,能隙渐变层的靠近于高折射率层的部分的能隙较小,而能隙渐变层的靠近于低折射率层的部分的能隙较大。能隙渐变层的能隙变化可以是线性渐变、非线性渐变、阶梯状渐变等帮助载子移动的适当能隙渐变方式。

[0026]

其中,能隙渐变层的材料为al

x

ga

1-x

as或al

x

ga

1-x

as

1-y

p

y

。

[0027]

当能隙渐变层设置于下dbr层时,能隙渐变层是设置于高折射率层与低折射率层之间,其中高折射率层在能隙渐变层之下,而低折射率层在能隙渐变层之上。

[0028]

当能隙渐变层设置于上dbr层时,能隙渐变层是设置于低折射率层与高折射率层之间,其中低折射率层在能隙渐变层之下,而高折射率层在能隙渐变层之上。

[0029]

在一实施例中,上述的主动区更包含两层或多层的主动层,较佳的,相邻的两主动层或每两相邻的两主动层之间设置内间隔层,相邻的两主动层间的内间隔层可包含al

x

ga

1-x

as

1-y

p

y

,其中在室温下al

x

ga

1-x

as

1-y

p

y

的晶格常数大于gaas基板的晶格常数。

[0030]

由于al

x

ga

1-x

as

1-y

p

y

材料与gaas基板之间晶格相对较为匹配,而使al

x

ga

1-x

as

1-y

p

y

产生的是压缩应力且压缩应力较小,因此能够减少vcsel中的压缩应力累积且避免产生明显的拉伸应力,进而增进vcsel组件的可靠度、降低组件制作的困难度或降低破片风险。

附图说明

[0031]

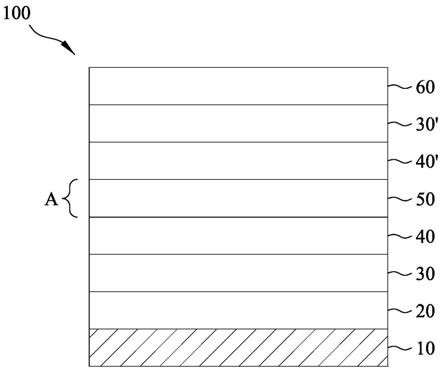

图1为依据被描述一实施例的vcsel结构示意图。

[0032]

图2为依据被描述一实施例的dbr层的结构示意图。

[0033]

图3为依据被描述一实施例的具有能隙渐变层的dbr层的结构示意图。

[0034]

图4为依据被描述一实施例的具有材料非均匀区的dbr层的结构示意图。

[0035]

图5与图6为比较例1的vcsel磊芯片的中心区域与边缘区域的xrt显像图。

[0036]

图7与图8为比较例2的vcsel磊芯片的中心区域与边缘区域的xrt显像图。

[0037]

图9与图10为依据一实施例的vcsel磊芯片的中心区域与边缘区域的xrt显像图。

[0038]

图11与图12为比较例3的vcsel磊芯片的中心区域与边缘区域的xrt显像图。

[0039]

附图标记说明

[0040]

10:基板

[0041]

20:缓冲层

[0042]

30:下dbr层

[0043]

30

’

:下dbr层

[0044]

31:低折射率层

[0045]

311:中间部分

[0046]

312:上侧部分

[0047]

313:下侧部分

[0048]

33:高折射率层

[0049]

35、35

’

:能隙渐变层

[0050]

40:下间隔层

[0051]

40

’

:上间隔层

[0052]

50:主动区

[0053]

60:欧姆接触层

[0054]

100:vcsel。

具体实施方式

[0055]

以下配合附图及附图标记对本发明的实施方式作更详细的说明,以使本领域技术人员在研读本说明书后能据以实施。为便于理解本发明,图式中仅绘制出激光二极管的部分结构,并非限制激光二极管仅由下述结构所构成。图式中各层之间的厚度比例也非实际比例,应根据实际需要而调整各层的厚度。

[0056]

以下描述具体的组件及其排列的例子以简化本发明。当然这些仅是例子且不该以此限定本发明的范围。例如,在描述中提及一层于另一层之上时,其可能包括该层与该另一层直接接触的实施例,也可能包括两者之间有其他组件或磊晶层形成而没有直接接触的实施例。此外,在不同实施例中可能使用重复的标号及/或符号,这些重复仅为了简单清楚地叙述一些实施例,不代表所讨论的不同实施例及/或结构之间有特定关联。

[0057]

此外,其中可能用到与空间相关的用词,像是“在...下方”、“下方”、“较低的”、“上方”、“较高的”及类似的用词,这些关系词是为了便于描述图式中一个(些)组件或特征与另一个(些)组件或特征之间的关系。这些空间关系词包括使用中或操作中的装置的不同方

位,以及图式中所描述的方位。

[0058]

本发明说明书提供不同的实施例来说明不同实施方式的技术特征。举例而言,全文说明书中所指的“一些实施例”意味着在实施例中描述到的特定特征、结构、或特色至少包含在一实施例中。因此,全文说明书不同地方所出现的片语“在一些实施例中”所指不一定为相同的实施例。

[0059]

此外,特定的特征、结构、或特色可在一或多个的实施例中通过任何合适的方法结合。进一步地,对于在此所使用的用语“包括”、“具有”、“有”、“其中”或前述的变换,这些语意类似于用语“包括”来包含相应的特征。

[0060]

此外,“层”可以是单一层或者包含是多层;而一磊晶层的“一部分”可能是该磊晶层的一层或互为相邻的多层。

[0061]

现有技术中,激光二极管可依据实际需求而选择性的设置缓冲层,且在一些实例中,缓冲层可与基板在材质是相同的。且缓冲层设置与否,跟以下实施例所欲讲述的技术特点与所欲提供的效果并无实质相关,因此为了简要示例说明,以下实施例仅以具有缓冲层的激光二极管来做为说明用的示例,而不另赘述没有设置缓冲层的激光二极管,也就是以下实施例如置换无缓冲层的激光二极管也能一体适用。

[0062]

参考图1,图1为依据被描述一实施例的vcsel结构示意图。如图1所示,vcsel100的结构由下而上包括gaas基板10、缓冲层20、下dbr层30、下间隔层40、包含主动层50的主动区a、上间隔层40

’

、上dbr层30

’

以及欧姆接触层60。缓冲层20、主动层50以及欧姆接触层60是使用习知的半导体材料,并且通过磊晶成长的方式而形成,在此该些结构的半导体材料则不赘述。图1中的主动区a包含一主动层50,但不限于此,主动区a也可包含两层或多层主动层,较佳的,相邻的两主动层或每两相邻的两主动层之间设置内间隔层(图未示)。

[0063]

参考图2,下dbr层30或上dbr层30

’

(以下或称为dbr层30、30

’

)的一种示范性结构是分别包含多层的低折射率层31及多层的高折射率层33,将低折射率层31及高折射率层33交替堆叠而形成周期性结构(periodic structures)。当堆叠的层数越多时,dbr层30、30

’

对特定波长的光线的总反射率越接近于100%,且低折射率层31与高折射率层33之间的折射率差异越大时,dbr层30、30

’

通常会有越高的总反射率。图2虽然仅显示3对的堆叠结构,但dbr层30、30

’

可根据所要求的总反射率而具有数十对堆叠结构。上述的一对堆叠结构是包含一层的低折射率层及一层的高折射率层,低折射率层可在高折射率层之上或之下,反之亦然。

[0064]

虽然图2中所显示的dbr层30、30

’

的最底层是高折射率层33,然后再与低折射率层31以交替堆叠方式形成多层结构;当然,dbr层30、30

’

的最底层也可以是低折射率层31,然后再与高折射率层33以交替堆叠方式形成多层结构。

[0065]

为了增加dbr层30、30

’

的总反射率,通常低折射率层31可选用包含高含量铝的材料,在一实施例中,包含高含量铝的材料可以是algaas;高折射率层33可选用包含低含量铝的材料或者不含铝的材料,在一实施例中,包含低含量铝的材料可以是algaas,而不含铝的材料可以是gaas;即,通过调整低折射率层与高折射率层之间的铝含量差异来改变dbr层30、30

’

的反射率。然而,algaas材料相对于gaas基板因彼此晶格不匹配,于是会产生较大的压缩应力,且dbr层30、30

’

通常为数十对的堆叠结构,因此所累积的压缩应力会导致磊芯片翘曲,或使vcsel100磊晶层中因累积过大的压缩应力而产生缺陷或差排,如此会导致vcsel

组件的可靠度不佳。

[0066]

为改善上述的问题,基本上可在多层低折射率层31的至少一部分中添加磷,或者是在多层高折射率层33的至少一部分中添加磷,又或者在多层低折射率层31与在多层高折射率层33的至少一部分中均添加磷,以使dbr层的压缩应力适度变小而能降低磊芯片的翘曲程度或减少或消除磊晶层的缺陷或差排。

[0067]

多层低(高)折射率层31的“至少一部分”中添加磷是指在多层低(高)折射率层中的“一层、二层、三层或被选择的数层”添加磷,如果有必要也可以在多层低(高)折射率层中“被选择的多数层”甚至每一层均添加磷。

[0068]

以前文所述的低折射率层31及/或高折射率层33的材质是algaas为例,当在低折射率层31及/或高折射率层33“添加磷”后,则低折射率层31及/或高折射率层33的材质会形成al

x

ga

1-x

as

1-y

p

y

,其中al

x

ga

1-x

as

1-y

p

y

的晶格常数在室温下大于该gaas基板的晶格常数。除了上dbr层与下dbr层以外,在主动区外的上间隔层、下间隔层或在主动区内的内间隔层也可使用al

x

ga

1-x

as

1-y

p

y

,其中al

x

ga

1-x

as

1-y

p

y

的晶格常数在室温下大于该gaas基板的晶格常数。

[0069]

上述的“添加磷”是指:在磊晶成长的过程中将磷元素或将磷元素连同其他元素注入反应腔中进行磊晶成长的步骤。al

x

ga

1-x

as

1-y

p

y

可减少该磊晶层与gaas基板10之间晶格不匹配的问题,也就是al

x

ga

1-x

as

1-y

p

y

与algaas的铝含量为一样下,al

x

ga

1-x

as

1-y

p

y

的晶格常数与gaas基板的晶格常数的差异会小于algaas的晶格常数与gaas基板的晶格常数的差异,进而适度减少压缩应力的累积,也就是让上dbr层、上间隔层、下间隔层、下dbr层或内间隔层具有适度的压缩应力,进而避免因为压缩应力总和过大而导致vcsel100产生翘曲、晶体缺陷或差排,也能避免al

x

ga

1-x

as

1-y

p

y

在室温下产生拉伸应力;此外,在上dbr层、上间隔层、下间隔层、下dbr层或内间隔层“添加磷”后,由于algaasp相对于algaas较不容易被氧化,因此在氧化处理时,algaasp磊晶层会被氧化的部分较少,则algaasp磊晶层的vcsel的应力也能适当变小,有助于改善vcsel的可靠度。要注意的是,al

x

ga

1-x

as

1-y

p

y

的晶格常数在室温下须大于gaas基板的晶格常数;较佳的,al

x

ga

1-x

as

1-y

p

y

的晶格常数与gaas基板的晶格常数之间要具有适当差距或适当余裕(margin),让al

x

ga

1-x

as

1-y

p

y

在磊晶成长过程中,即使长晶温度较高,al

x

ga

1-x

as

1-y

p

y

仍然是产生压缩应力或避免产生明显拉伸应力,以改善vcsel组件的可靠度或减少vcsel磊芯片的形变。

[0070]

当低折射率层31及高折射率层33之间的折射率差异越大时,dbr层30、30

’

对于特定波长的反射率也能提高。其中,低折射率层31及/或高折射率层33中的al

x

ga

1-x

as

1-y

p

y

铝含量可为0<x≦1,只要低折射率层31的铝含量高于高折射率层33的铝含量即可。较佳地,低折射率层31的铝含量可为0.7≦x≦1,且高折射率层33的铝含量可为0<x≦0.5,通过调整铝的含量,可使低折射率层31及高折射率层33之间的折射率差异扩大,而提高dbr层30、30

’

的总反射率。当折射率差异越大时,亦可减少dbr层30、30

’

中堆叠层数,使其总厚度减小并且保有一定的总反射率。

[0071]

以低折射率层31为例,在algaas或algaasp中提高铝含量可降低折射率,但也会产生更多的压缩应力。在algaas添加磷或在algaasp提高磷含量可减少铝所产生的压缩应力。当algaasp中磷的添加量与铝的添加量成正相关时,algaasp的压缩应力或晶格常数不易改变。但磷的添加量应适量,因磷的添加量太多则反而会有折射率改变,或因晶格常数等于或

小于gaas基板时反而在磊晶成长时产生拉伸应力等的问题,因此低折射率层31的al

x

ga

1-x

as

1-y

p

y

中磷的含量范围可约为0<y≦0.03,其中磷的含量可以是0.03、0.025、0.024、0.023、0.022、0.021、0.02、0.019、0.018、0.017、0.016、0.015、0.013、0.01或0.007。高折射率层33的al

x

ga

1-x

as

1-y

p

y

中磷的含量范围可为0<y≦0.015,其中磷的含量可以是0.015、0.01、0.008、0.007、0.0065、0.006、0.0055、0.005、0.0045、0.004、0.0035、0.003、0.002或0.001。al

x

ga

1-x

as

1-y

p

y

中磷的含量可通过x光谱来测定,其测试对象可以是在gaas基板上磊晶成长一层固定铝及镓含量的al

x

ga

1-x

as

1-y

p

y

磊晶层或vcsel磊芯片。

[0072]

原则上,当高折射率层产生拉伸应力时,可以适度调整低折射率层的磷添加量,以使低折射率层产生压缩应力;因此低折射率层所产生的压缩应力能对高折射率层的拉伸应力作应力补偿,而降低dbr层的应力总和。

[0073]

由于低折射率层31中的铝含量大于高折射率层33的铝含量,因此低折射率层31中添加的磷含量可大于高折射率层33的磷含量。

[0074]

若下dbr层30为n型dbr层时,则上dbr层30

’

可为p型dbr层,也可根据需要将n型、p型对调,只要dbr层30、30

’

的其中一者为n型dbr层且另一者为p型dbr层,形成一个p-n二极管结构即可。材料为al

x

ga

1-x

as

1-y

p

y

的低折射率层31及/或高折射率层33可设置在n型dbr层或是设置在p型dbr层,或者n型dbr层与p型dbr层的低折射率层31及高折射率层33的材料皆是al

x

ga

1-x

as

1-y

p

y

。

[0075]

当n型dbr层与p型dbr层的低折射率层31及高折射率层33的材料皆是al

x

ga

1-x

as

1-y

p

y

时,可减少dbr层30、30

’

中所产生的压缩应力,以减少vcsel100中的压缩应力累积。

[0076]

在n型dbr层设有al

x

ga

1-x

as

1-y

p

y

低折射率层31时,亦可减少vcsel100中的压缩应力累积。其中,提高al

x

ga

1-x

as

1-y

p

y

低折射率层31的磷含量也会提高低折射率层31的能隙,此能隙的提高对在导电带上移动的电子没有明显影响,因此可以仅在n型dbr层中设有材料为al

x

ga

1-x

as

1-y

p

y

的低折射率层31。在p型dbr层设有材料为al

x

ga

1-x

as

1-y

p

y

的高折射率层33时,亦可相对减少vcsel100中的压缩应力累积。其中,提高al

x

ga

1-x

as

1-y

p

y

高折射率层31的磷含量也会提高高折射率层33的能隙,此能隙的提高对在价电带上移动的电洞没有明显影响,因此可以仅在p型dbr层中设有材料为al

x

ga

1-x

as

1-y

p

y

的高折射率层33。

[0077]

低折射率层31或高折射率层33的至少一部分是al

x

ga

1-x

as

1-y

p

y

是指:可在低铝含量的algaas中添加磷元素及/或在高铝含量的algaas中添加磷元素。较佳地,可仅在高铝含量的algaas中添加磷元素,以将由高铝含量所造成的较大压缩应力适当降低。当高折射率层33由低铝含量的algaas或gaas组成时,由于高折射率层的压缩应力较小,亦可无需添加磷元素。

[0078]

此外,还可在多层的低折射率层31中选取特定数层进行磷元素的添加。例如,dbr层30、30

’

在分别由40组周期性结构组成的情况下,可在40层的低折射率层31中选择40层、30层或20层添加磷元素,但层数并不限于此,可根据所欲降低压缩应力的程度而调整需要添加磷的层数。同样地,在高折射率层33中添加磷元素时,也可根据需要选取特定层数进行磷元素的添加。

[0079]

针对单一层的由al

x

ga

1-x

as

1-y

p

y

组成的低折射率层31或高折射率层33,若在磊晶成长的全程导入恒定浓度的磷元素时,则可形成al

x

ga

1-x

as

1-y

p

y

的含磷浓度为大致均匀分布的材料均匀区。

[0080]

在一实施例,材料非均匀区的一部分区域可以是al

x

ga

1-x

as

1-y

p

y

,而其他区域则为al

x

ga

1-x

as,例如,在形成单一层的低折射率层31的过程中,仅在1/3的al

x

ga

1-x

as磊晶制作期间内导入磷元素,于是材料非均匀区的约1/3区域为al

x

ga

1-x

as

1-y

p

y

,而其余的2/3区域为al

x

ga

1-x

as;在一实施例中,如果材料非均匀区的材料都是al

x

ga

1-x

as

1-y

p

y

,也可以通过使材料非均匀区中的至少两部分的含磷浓度不相同,而使材料非均匀区的不同部分有不同的含磷浓度。在一实施例中,材料非均匀区的中间部分是al

x

ga

1-x

as

1-y

p

y

,在中间部分之上的上侧部分与在中间部分之下的下侧部分为al

x

ga

1-x

as,中间部分在低折射率层中的实际厚度可根据需要来作调整。

[0081]

在上述的说明中,若低折射率层31中铝含量为0.7≦x≦1时,其能隙较大,高折射率层33中铝含量为0<x≦0.5时,其能隙相对较小,当低折射率层与高折射率层之间的铝含量有差异时,会在低折射率层及高折射率层之间的接面产生导电带(conduction band)及价电带(valance band)的不连续,于是载子(carrier)在流动时会遭遇较大的位障(potentilal barrier height),导致电阻上升。

[0082]

如图3所示,在dbr层30及/或dbr层30

’

中还可分别包含设置在低折射率层31及高折射率层33之间的能隙渐变层35、35

’

,能隙渐变层35、35

’

可包含al

x

ga

1-x

as或al

x

ga

1-x

as

1-y

p

y

;其中,能隙渐变层的能隙会逐渐变化,原则上,能隙渐变层靠近于高折射率层的部分的能隙相对较低,而能隙渐变层靠近于低折射率层的部分的能隙相对较高;能隙渐变层的能隙变化可以是选自由线性渐变、非线性渐变、阶梯状渐变及其他帮助载子移动的适当能隙渐变方式所组成的群组。

[0083]

能隙渐变可以通过调整材料的成分或通过其他适当方式来达成,以al

x

ga

1-x

as为例,可以通过调整铝或镓的含量多寡来使能隙渐变,比如铝的含量可在低折射率层31往高折射率层33的方向上由多逐渐变少。例如,图3中能隙渐变层35的铝含量在由下往上的方向上由少逐渐变多,且能隙渐变层35

’

的铝含量在由下往上的方向上为由多逐渐变少,从而使导电带及价电带能阶产生渐变,进而降低或消除低折射率层31与高折射率层33之间的载子位障,避免电阻上升。例如低折射率层31中铝的含量为x=0.9且高折射率层33中铝的含量x=0.1,能隙渐变层35、35

’

的铝含量可约为0.1≦x≦0.9,且其铝含量可在低折射率层31往高折射率层33的方向上逐渐变少。能隙渐变层35、35

’

中铝含量的上限值及下限值并未限制在需与低折射率层31及高折射率层33中的铝含量完全一致,可在未显着影响电阻的情况下进行调整。

[0084]

以al

x

ga

1-x

as

1-y

p

y

为例,除了调整单一元素(铝、镓或磷)的含量外,也能通过调整多种元素的含量(铝与磷或铝与镓等),而使能隙渐变层的能隙逐渐变化。

[0085]

图3所示是一种较佳实施结构;由于n型的dbr层不同于p型的dbr层,原则上可以仅在高折射率层33与低折射率层31之间设置能隙渐变层35,或者只在低折射率层31与高折射率层33之间设置能隙渐变层35。

[0086]

具体而言,在下dbr层为n型时,高折射率层在下时而低折射率层在上时,只要在下为高折射率层与上为低折射率层之间处设置能隙渐变层即可。至于下为低折射率层与上为高折射率层之间是否需设置能隙渐变层,则视实际需求而定。

[0087]

而在上dbr层为p型时,当低折射率层在下而高折射率层在上时,只要在下为低折射率层与上为高折射率层之间处设置能隙渐变层即可。然而上为低折射率层与下为高折射

率层之间是否需设置能隙渐变层,则视实际需求而定。

[0088]

参阅图4,图4与图3的结构是相同的,只是图4中的低折射率层31设置材料非均匀区;且材料非均匀区包含介于上侧部分312与下侧部分313之间的中间部分311;较佳的,中间部分311的材料为al

x

ga

1-x

as

1-y

p

y

,而上侧部分312、下侧部分313的材料为al

x

ga

1-x

as;通过材料非均匀区的设置、材料非均匀区及能隙渐变层的配合设置或材料均匀区及能隙渐变层的配合设置,能据以降低或消除低折射率层31与高折射率层33之间的载子位障,避免电阻上升。

[0089]

图4所显示的高折射率层33与低折射率层31都设置材料非均匀区;在一些实施例中,可以根据实际需求而仅在低折射率层31或高折射率层33中设置材料非均匀区或者设置材料均匀区。

[0090]

通过以上的说明,通过以晶格常数在室温时是大于gaas基板的al

x

ga

1-x

as

1-y

p

y

作为dbr层或间隔层,可适度的减少dbr层或间隔层的压缩应力总和,以使dbr层或间隔层在室温下具有适当的压缩应力,且能避免dbr层或间隔层在磊晶成长时产生明显的拉伸应力,如此较能避免vcsel磊芯片发生变形翘曲、缺陷或差排的问题,借以增进vcsel组件可靠度、改善制程良率或降低破片率。

[0091]

此外,还可将能隙渐变层设置于dbr层的低折射率层及高折射率层之间,降低或消除低折射率层与高折射率层之间的载子位障,避免电阻上升。

[0092]

在本说明书,vcsel磊晶层中的缺陷或差排是以xrt显像(x-ray topography)呈现,以呈现比较例1、2、3与一实施例的差排。比较例1、2、3与本文的一实施例的主要结构与图1的vcsel相同,只有上dbr层与下dbr层的低折射率层的材料成分不同,材料成分中的铝含量相同但磷含量不同。其他的磊晶层的材料成分是大致相同,基板皆为gaas。

[0093]

图5与图6是对应比较例1的vcsel,其中,上dbr层与下dbr层的低折射率层是algaasp,在室温下algaasp的晶格常数小于gaas基板的晶格常数,因此algaasp在室温下会产生拉伸应力与在磊晶成长时会产生较大的拉伸应力;观察图5与图6的量测结果,图5与图6出现较多的明显暗线,暗线代表差排(dislocation)。

[0094]

图7与图8是对应比较例2的vcsel,其中,上dbr层与下dbr层的低折射率层是algaasp,在室温下algaasp的晶格常数是等于gaas基板。观察图8与图9的量测结果,发现图7与图8中出现多条的明显暗线,且在vcsel磊芯片的边缘区域(图8)中的暗线多于vcsel磊芯片的中心区域(图7)的暗线数量。原因之一是,在室温下algaasp晶格常数即使能匹配于gaas基板,但长晶过程中的温度远高于室温,且algaasp与gaas基板的热膨胀系数不同,因此在温度较高的环境下algaasp层会产生拉伸应力。另一原因是现有磊晶成长技术尚无法使磊晶层各处的材料成分完全均匀一致;当algaasp磊晶层的中心区域的晶格常数等于gaas基板的晶格常数时,则algaasp磊晶层的边缘部分的晶格常数通常会小于gaas基板的晶格常数。algaasp磊晶层的边缘部分的晶格常数较中间区域小是因为边缘区域的含磷量较中心区域多。含磷量较多的部分因晶格常数小于gaas基板因而已具有拉伸应力,由于磊晶成长时温度远高于室温,因此algaasp磊晶层的含磷量较多的部分的拉伸应力会更大。

[0095]

图9与图10对应本文的一实施例的vcsel,其中,以algaasp作为上dbr层与下dbr层的低折射率层,在室温下algaasp的晶格常数是略大于gaas基板的晶格常数,因此algaasp在磊晶成长时不容易产生应力或产生适当的压缩应力。观察图9与图10的量测结果,在图9

与图10没有观察到暗线的存在。

[0096]

图11与图12是对应比较例3的vcsel,其中,以algaas作为上dbr层与下dbr层的低折射率层,在室温下algaas的晶格常数是大于gaas基板的晶格常数(algaasp的铝含量与algaas的铝含量相同),因此algaas会产生较大的压缩应力。从图11与图12的量测结果也可观察到一些暗线。由此可知,磊晶层虽产生的是压缩应力,但压缩应力过大,磊晶层仍是会发生较多的缺陷或差排。

[0097]

根据839案的教示所作出的vcsel,实际上磊晶成长时磊晶层因会产生拉伸应力,较容易使磊晶层发生严重的缺陷或差排,从而导致vcsel的可靠度变差;与829案的教示正好相反,当磊晶层在磊晶成长时不产生应力或产生适度的压缩应力,vcsel的可靠度实际上能得到明显增进。

[0098]

以上所述者仅为用以解释本发明的较佳实施例,并非企图据以对本发明做任何形式上的限制,是以,凡有在相同的发明精神下所作有关本发明的任何修饰或变更,皆仍应包括在本发明意图保护的范畴。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1