一种氮化镓金属氧化物半导体晶体管及其制备方法与流程

1.本发明涉及氮化镓功率半导体器件,尤其是一种高阻断电压的氮化镓mosfet结构,属于电力电子器件技术领域。

背景技术:

2.氮化镓材料具有高的击穿电场、高的饱和速度、好的散热性能,相比于硅基场效应晶体管,氮化镓场效应晶体管具有高耐压,低导通电阻,寄生参数小等优异特性,当应用于开关电源领域中,具有损耗小,工作频率高,可靠性高等优点,可以大大提升开关电源的效率,功率密度和可靠性等性能。

3.现行技术中的氮化镓mosfet主要包括基于gan体材料的垂直型mosfet和基于二维电子气(2deg) 的algan/gan 等异质结的横向型hmet。

4.现行技术中的横向型氮化镓hemt一般通过加大极间间距以增大漂移区长度获得较大的阻断电压,但因此会增大器件的芯片面积,且制作在异质衬底上的氮化镓外延层的缺陷密度较大以及难以获得较大厚度的外延层,影响器件阻断电压、导通电阻等性能的提高。

5.垂直型氮化镓mosfet制作在同质外延的氮化镓半导体层上,结构包括自下而上依次相接的源极电极和栅极电极、衬底、器件结构层、漏极电极。现行技术中的垂直型氮化镓mosfet一般通过增加漂移区厚度提高阻断电压,实现高功率密度。但氮化镓外延半导体层的缺陷密度与外延层的厚度成正比,较大厚度的氮化镓半导体外延层中的缺陷密度较大,影响器件关键的阻断电压和反向漏电流性能指标的提高,而现行氮化镓外延技术在性能、成本和尺寸上的不足限制了基于自支撑氮化镓衬底的氮化镓mosfet器件的制备与应用。

6.并且,垂直型氮化镓mosfet总体上为一种体结构mosfet,输入输出电极分别位于结构的顶部和底部,构成一种垂直的载流子漂移或电流通道,而准垂直型的氮化镓mosfet通过台面结构暴露位于底部的漂移层,引出输出电极,均为非共面的输入输出电极结构,不便于器件的平面集成以及在功率集成电路中的应用。

技术实现要素:

7.本发明针对以上问题,提供了一种采用环状漂移区结构,增大器件结构中漂移区的长度以提高器件的阻断电压,同时使器件的栅极电极、源极 电极、漏极电极汇集于其结构的顶面,形成共面的器件输入输出电极结构,便于器件的平面集成的一种氮化镓金属氧化物半导体晶体管。

8.本发明的技术方案是:一种氮化镓金属氧化物半导体晶体管的制备方法,包括以下步骤:1)准备基板;2)在基板上淀积0.5μm厚的aln过渡层;3)在所述过渡层上淀积8μm厚的n

―

‑

gan漂移层,si掺杂浓度为1

×

10

16 cm

‑3;

4)采用mocvd方法在所述漂移层上淀积0.5μm厚的n

+

‑

gan欧姆接触层,si掺杂浓度为6

×

10

19 cm

‑3;,5)采用深反应离子干法刻蚀法刻蚀漂移通道欧姆接触层和漂移层,形成漂移通道内隔离层沟槽和漂移通道外隔离层沟槽;6)采用等离子体增强化学气相沉积方法淀积二氧化硅或者氮化硅填充漂移通道内隔离层沟槽和漂移通道外隔离层沟槽,形成漂移通道内隔离层和漂移通道外隔离层;7)刻蚀漂移通道内隔离层之间的n+

‑

gan欧姆接触层和n

―

‑

gan漂移层形成有源区凹槽;8)有源区凹槽内再生长连通漂移层的3μm厚的n

―

‑

gan有源区第三半导体层,si掺杂浓度为1

×

10

16 cm

‑3;9)在有源区第三半导体层上生长1μm厚的p

‑

gan有源区第二半导体层,mg掺杂浓度为3

×

10

19 cm

‑3;10)在有源区第二半导体层上生长1μm厚的n

‑

gan有源区第一半导体层,si掺杂浓度为1

×

10

18 cm

‑3;11)在上述有源区第一半导体层上生长0.5μm厚的n

+

‑

gan有源区欧姆接触层,si掺杂浓度为6

×

10

19 cm

‑3;12)刻蚀n

+

‑

gan有源区欧姆接触层、n

‑

gan有源区第一半导体层、p

‑

gan有源区第二半导体层和n

―

‑

gan有源区第三半导体层,形成栅极绝缘层凹槽;13)淀积二氧化硅或者氮化硅填充栅极绝缘层凹槽,形成栅极绝缘层;14)刻蚀所述栅极绝缘层的中部,形成栅极沟槽;15)采用光刻方法形成用于栅极沟槽金属淀积的光刻胶掩模层,并采用电子束溅射或者磁控溅射方法淀积ti/au填充栅极沟槽,形成栅极;16)采用光刻方法形成用于栅极电极、源极电极和漏极电极金属淀积的光刻胶掩模层,并采用电子束溅射或者磁控溅射方法淀积ti/al/ti/au多金属层;通过剥离方法形成栅极电极、源极电极、漏极电极;17)600℃,n2气氛中退火形成源极电极、漏极电极与相应半导体层的欧姆接触。

9.一种氮化镓金属氧化物半导体晶体管,包括基板、过渡层、漂移层、有源区、栅极区、漂移通道和金属电极层;所述基板、过渡层和漂移层自下而上依次相接设置;所述有源区相接于漂移通道与漂移层之间;所述有源区包括自下而上依次相接的有源区第三半导体层、有源区第二半导体层、有源区第一半导体层、有源区欧姆接触层;所述栅极区包括栅极和栅极绝缘层;所述栅极绝缘层内嵌于有源区中;所述栅极内嵌入于栅极绝缘层中;所述漂移通道包括自下而上依次相接的通道漂移层、漂移通道欧姆接触层以及位于通道漂移层与漂移通道欧姆接触层内侧的漂移通道内隔离层和外侧的漂移通道外隔离层;所述有源区的两侧设有两个所述漂移通道,所述漂移通道通过漂移通道内隔离层与有源区相隔离;

所述金属电极层包括源极电极、漏极电极和栅极电极;所述源极电极位于有源区的顶部并与有源区欧姆接触层相接;所述漏极电极位于漂移通道的顶部并与漂移通道欧姆接触层相接;所述栅极电极位于栅极绝缘层和栅极的顶部并与栅极相接。

10.所述基板为si基板、sic基板或蓝宝石基板。

11.所述过渡层包括aln外延层。

12.还包括设置与所述aln外延层上的algan外延层。

13.所述有源区第一半导体层为n

‑

gan外延层或p

‑

gan外延层;所述有源区第二半导体层为p

‑

gan外延层或n

‑

gan外延层;所述有源区第三半导体层、漂移层、通道漂移层为n

―

‑

gan外延层或p

―

‑

gan外延层;所述有源区欧姆接触层和漂移通道欧姆接触层为n

+

‑

gan外延层或p

+

‑

gan外延层。。

14.所述漂移通道内隔离层、漂移通道外隔离层和栅极绝缘层分别为二氧化硅层或者氮化硅层。

15.所述栅极为ti/au双金属层或ni/au双金属层。

16.所述源极电极、漏极电极和栅极电极分别为ti/al/ti/au多金属层或cr/al/ti/au多金属层。

17.本发明中包括基板、过渡层、漂移层、有源区、栅极区、漂移通道和金属电极层;有源区第三半导体层、漂移层和两个漂移通道构成一个环状的漂移区结构,相对于仅有垂直漂移区的垂直型氮化镓mosfet器件结构,或者仅有横向漂移区的横向型氮化镓hemt器件结构,本发明中的漂移区的路径总长度大于制作在相同基板及外延层尺寸的垂直型器件结构的氮化镓mosfet或者横向型器件结构的氮化镓hemt中漂移区的路径的长度,由此增大氮化镓mosfet器件的阻断电压。本发明具有增大器件结构中漂移区的长度以提高器件的阻断电压,同时使器件的栅极电极、源极 电极、漏极电极汇集于其结构的顶面,形成共面的器件输入输出电极结构,便于器件的平面集成等特点。

附图说明

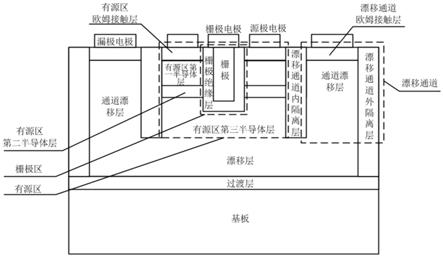

18.图1是本发明的结构示意图,图2是本发明步骤4)的结构示意图,图3是本发明步骤6)的结构示意图,图4是本发明步骤11)的结构示意图,图5是本发明步骤12)的结构示意图,图6是本发明步骤15)的结构示意图,图7是本发明步骤17)的结构示意图。

具体实施方式

19.下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,仅用于解释本发明,而不能理解为对本发明的限制。

20.本发明如图1

‑

7所示,一种氮化镓金属氧化物半导体晶体管的制备方法,包括以下

步骤:1)准备6英寸的si基板、sic基板或者蓝宝石基板;2)采用金属有机化学气相沉积(mocvd)方法在基板上淀积0.5μm厚的aln过渡层;3)采用mocvd方法在所述过渡层上淀积8μm厚的n

―

‑

gan漂移层,si掺杂浓度为1

×

10

16 cm

‑3(含漂移通道层);4)采用mocvd方法在所述漂移层上淀积0.5μm厚的n

+

‑

gan欧姆接触层,si掺杂浓度为6

×

10

19 cm

‑3;,如图2所示;5)采用反应离子刻蚀(rie)或者感应耦合等离子体(icp)等深离子干法刻蚀法刻蚀漂移通道欧姆接触层和部分或全部漂移层,形成漂移通道内隔离层沟槽和漂移通道外隔离层沟槽;6)采用等离子体增强化学气相沉积(pecvd)方法淀积二氧化硅或者氮化硅填充漂移通道内隔离层沟槽和漂移通道外隔离层沟槽,形成漂移通道内隔离层和漂移通道外隔离层,如图3所示;7)采用rie或者icp方法刻蚀两个漂移通道内隔离层之间的n

+

‑

gan欧姆接触层和部分n

―

‑

gan漂移层形成有源区凹槽;8)采用mocvd方法在有源区凹槽内再生长连通漂移层的3μm厚的n

―

‑

gan有源区第三半导体层,si掺杂浓度为1

×

10

16 cm

‑3;9)采用mocvd方法在有源区第三半导体层上生长1μm厚的p

‑

gan有源区第二半导体层,mg掺杂浓度为3

×

10

19 cm

‑3;10)采用mocvd方法在有源区第二半导体层上生长1μm厚的n

‑

gan有源区第一半导体层,si掺杂浓度为1

×

10

18 cm

‑3;11)采用mocvd方法在上述有源区第一半导体层上生长0.5μm厚的n

+

‑

gan有源区欧姆接触层,si掺杂浓度为6

×

10

19 cm

‑3;如图4所示;12)icp方法刻蚀n

+

‑

gan有源区欧姆接触层、n

‑

gan有源区第一半导体层、p

‑

gan有源区第二半导体层和部分n

―

‑

gan有源区第三半导体层,形成栅极绝缘层凹槽,如图5所示;13)采用pecvd方法淀积二氧化硅或者氮化硅填充栅极绝缘层凹槽,形成栅极绝缘层;14)采用rie或者icp方法刻蚀所述栅极绝缘层的中部,形成栅极沟槽;15)采用光刻方法形成用于栅极沟槽金属淀积的光刻胶掩模层,并采用电子束溅射或者磁控溅射方法淀积ti/au填充栅极沟槽,形成栅极,如图6所示;16)采用光刻方法形成用于栅极电极、源极电极和漏极电极金属淀积的光刻胶掩模层,并采用电子束溅射或者磁控溅射方法淀积ti/al/ti/au多金属层;通过剥离方法形成栅极电极、源极电极、漏极电极;17)600℃,n2气氛中退火形成源极电极、漏极电极与相应半导体层的欧姆接触,如图7所示。

21.一种氮化镓金属氧化物半导体晶体管,包括基板、过渡层、漂移层、有源区、栅极区、漂移通道和金属电极层;所述基板、过渡层和漂移层自下而上依次相接设置;所述有源区相接于两个漂移通道与漂移层(有源区与漂移层的上端相接)之间;

所述有源区包括自下而上依次相接的有源区第三半导体层、有源区第二半导体层、有源区第一半导体层、有源区欧姆接触层;所述栅极区包括栅极和栅极绝缘层;所述栅极绝缘层内嵌于有源区中;所述栅极内嵌入于栅极绝缘层中;各个所述漂移通道包括自下而上依次相接的通道漂移层、漂移通道欧姆接触层以及位于通道漂移层与漂移通道欧姆接触层内侧的漂移通道内隔离层和外侧的漂移通道外隔离层;所述有源区的两侧设有两个所述漂移通道,所述漂移通道通过漂移通道内隔离层与有源区相隔离;所述金属电极层包括源极电极、漏极电极和栅极电极;所述源极电极位于有源区的顶部并与有源区欧姆接触层相接;所述漏极电极位于漂移通道的顶部并与漂移通道欧姆接触层相接;所述栅极电极位于栅极绝缘层和栅极的顶部并与栅极相接。

22.所述基板为si基板、sic基板或蓝宝石基板。

23.所述过渡层包括aln外延层。

24.还包括设置与所述aln外延层上的algan外延层,即过渡层包括自下而上相接的aln外延层和algan外延层。

25.所述有源区第一半导体层为n

‑

gan外延层,用作本发明的氮化镓金属氧化物半导体晶体管的源区;所述有源区第二半导体层为p

‑

gan外延层,用作本发明的氮化镓金属氧化物半导体晶体管的沟道区;所述有源区第三半导体层、漂移层、通道漂移层为n

―

‑

gan外延层,用作本发明的氮化镓金属氧化物半导体晶体管的漏区(漂移层);所述有源区欧姆接触层和漂移通道欧姆接触层为n

+

‑

gan外延层,用以形成本发明的氮化镓金属氧化物半导体晶体管的源极电极、漏极电极的欧姆接触。

26.所述漂移通道内隔离层、漂移通道外隔离层和栅极绝缘层分别为二氧化硅层或者氮化硅层。

27.所述栅极为ti/au双金属层或ni/au双金属层。

28.所述源极电极、漏极电极和栅极电极分别为ti/al/ti/au多金属层或cr/al/ti/au多金属层。

29.本发明中的有源区第一半导体层、有源区第二半导体层、所述有源区第三半导体层分别作为源区、沟道区和漏区(漂移层)构成本发明的氮化镓金属氧化物半导体晶体管(mosfet)有源区结构,栅极电极控制沟道区使mosfet导通或截止。反向偏置时,氮化镓金属氧化物半导体晶体管因氮化镓材料所具有的大禁带宽度、高击穿电场特点而具有较高的阻断电压,并且由于本发明特有的环状漂移区的路径总长度大于制作在相同尺寸的基板及外延层上的横向型器件结构或者垂直型器件结构的氮化镓金属氧化物半导体晶体管中作为漏区的漂移区的路径长度,由此进一步提高氮化镓金属氧化物半导体晶体管的阻断电压,同时使器件的栅极电极、源极电极、漏极电极汇集于其结构的顶面,形成共面的器件输入输出电极结构,便于实现器件的平面集成以及在功率集成电路中的应用。

30.本发明中的有源区第三半导体层、漂移层和两个漂移通道构成一个环状的漂移区结构,相对于仅有垂直漂移区的垂直型氮化镓mosfet器件结构,或者仅有横向漂移区的横向型氮化镓hemt器件结构,本发明中的漂移区的路径总长度大于制作在相同基板及外延层尺寸的垂直型器件结构的氮化镓mosfet或者横向型器件结构的氮化镓hemt中漂移区路径长度,由此增大氮化镓mosfet器件的阻断电压。

31.相比于要求较厚垂直漂移区的垂直型氮化镓mosfet或者要求较长横向漂移区的横向型氮化镓hemt,本发明特有的环状电流漂移区结构不要求较长或者较厚的外延层,可以利用现行技术中工艺比较成熟,成本比较低廉的硅基氮化镓衬底材料制作高阻断电压的氮化镓功率器件,满足大规模应用的需求。

32.同时,本发明特有的环状电流漂移区结构,可以使器件的栅极电极、源极电极、漏极电极汇集于结构的顶面,即本发明的氮化镓mosfet具有共面的输入输出电极结构特点,便于实现器件的平面集成化以及应用于功率集成电路中。

33.本发明的各个结构要素呈圆形或者任意多边形结构,相应地,本发明的器件芯片外形呈圆形或者任意多边形。

34.对于本案所公开的内容,还有以下几点需要说明:(1)、本案所公开的实施例附图只涉及到与本案所公开实施例所涉及到的结构,其他结构可参考通常设计;(2)、在不冲突的情况下,本案所公开的实施例及实施例中的特征可以相互组合以得到新的实施例;以上,仅为本案所公开的具体实施方式,但本公开的保护范围并不局限于此,本案所公开的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1