半导体器件及其制备方法、电子设备与流程

本发明涉及半导体,特别涉及一种半导体器件及其制备方法、电子设备。

背景技术:

1、现有半导体芯片衬底在衬底及外延片表面是各向同性的,也即不同衬底表面上各个位置上的垂直结构和电性能是相同的。这样做的原因主要是基于成本方面的考虑,在衬底进行mocvd(金属有机化合物化学气相沉淀)或mbe(分子束外延)外延生长的时候,把多个衬底放入反应炉中一起生长,由于生长气体的化学反应产生的外延生长在反应炉内的各个衬底表面基本相同,因此生长出的外延片结构也是相同的。

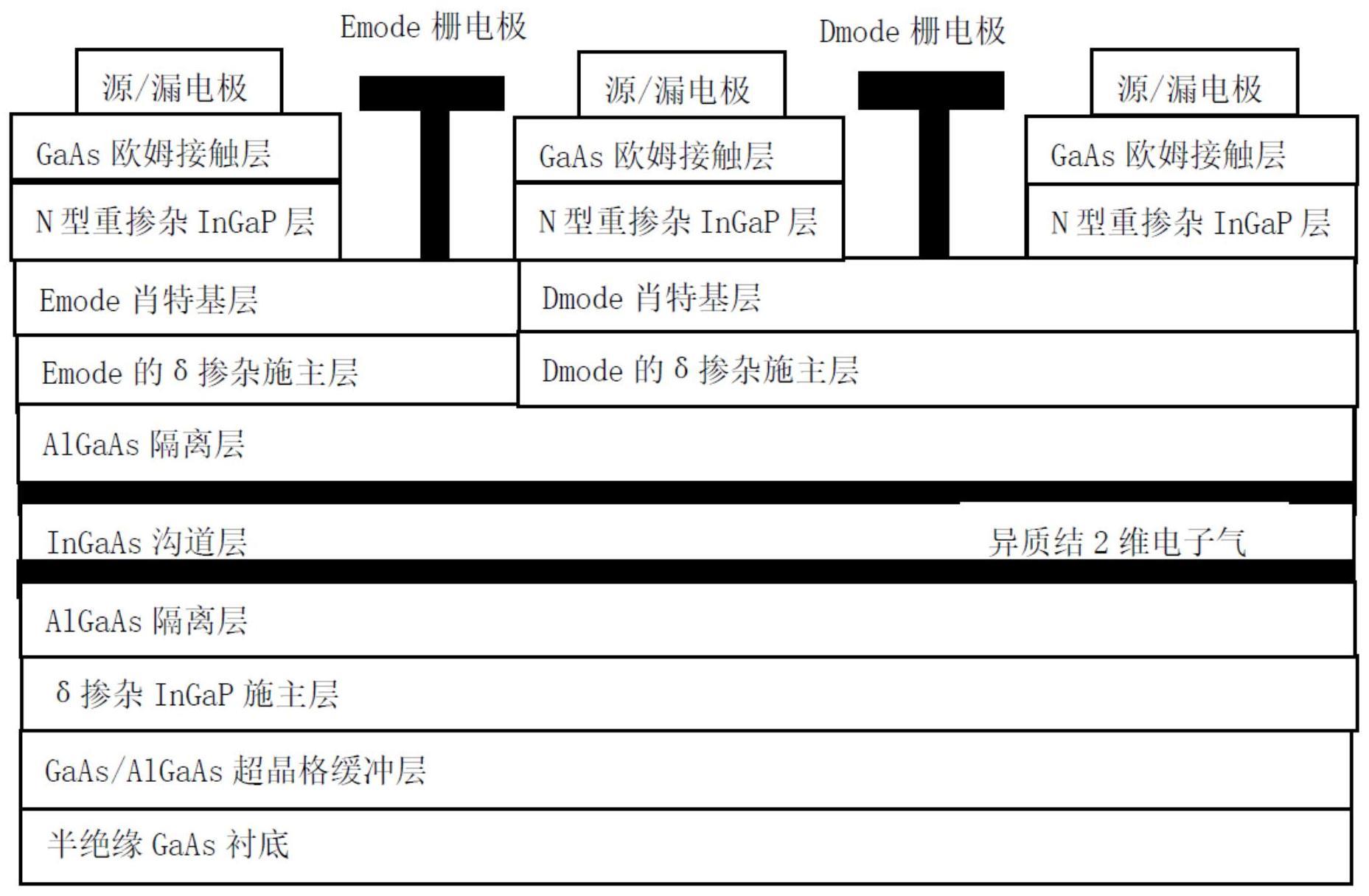

2、芯片工艺总是追求更高的集成度,以获得更高性能、更便宜的价格以及更高的可靠性。以phemt(pseudomorphic hemt,赝调制掺杂异质结场效应晶体管)结构的将dmode(耗尽型)工艺和emode(增强型)工艺集成在一个衬底外延片上为例,在如图1所示的采用gaas衬底的phemt结构中,dmode开关栅下有dmode肖特基层以及emode肖特基层,而emode开关栅下仅有emode肖特基层。由于工艺不同,现有技术制作的各向同性衬底外延片上emode和dmode的栅极高度不同,dmode栅极下肖特基层更厚,导致在该肖特基层中存在“耗尽区”(depletion),该区没有活动的电子电荷。该种结构导致dmode栅极阈值低于0v,也即dmode晶体管在不加栅电压控制时,源极漏极处于打开状态。而emode栅极下肖特基层更薄,导致在该肖特基层中没有“耗尽区”。该种结构导致dmode栅极阈值高于0v,也即emode晶体管在不加栅电压控制时,源极漏极处于关闭状态。现有dmode工艺集成的外延片能带结构如图2(a)所示,emode工艺集成的外延片能带结构如图2(b)所示。

3、通常情况下,为了工艺方便,现有技术采用dmode栅下肖特基层与emode栅下肖特基层相同化学组分的材料,在制作emode栅极时,刻蚀掉一部分栅下肖特基层,制作dmode栅极时,不刻蚀栅下肖特基层。结果是dmode和emode栅极高度不一致,也造成了低处的emode栅极难以制作“t型栅”(t-gate)。

4、对phemt结构而言,理论及实验均表明t型栅对提升芯片性能有重要好处。因此当前水平方向各向同性衬底外延片技术上制作的异质工艺集成dmode和emode芯片,性能有所折中,难以对dmode和emode区域同时优化,通常照顾了dmode区域,在高处的dmode实现t型栅,而牺牲了低处的emode区域,在低处的emode放弃了t型栅,只能采用梯形栅。这种方案存在以下问题:

5、第一、工艺复杂性增加,工艺要求非常高,良率和可靠性下降;

6、现有技术制作的衬底外延片需要先刻蚀掉其它工艺的衬底,保留自己工艺的衬底结构,不但造成工艺复杂性增加,而且使可靠性下降。例如制作emode栅极时,由于要在当前集成emode和dmode的衬底中刻蚀掉dmode肖特基层,在不同高度生长emode栅极,增加了工艺复杂性,而且要求高质量的刻蚀界面。不但对刻蚀工艺要求非常高,屏蔽了干法刻蚀等某些高速高效但难以形成高质量界面的刻蚀技术,而且可能还需要增加新的抛光工艺,严重降低了emode栅极的良率和可靠性。

7、第二、性能下降;

8、由于emode栅极沉降在dmode肖特基层之间,因此emode栅极难以制作类似dmode栅极的t型栅(t-gate)类似的场板(fieldplate)结构。仿真和试验均证明,场板结构可以有效降低低噪声放大器lna的噪声系数,提高增益,并降低功耗、提升效率。现有技术后续也发展了单独的emode的t型栅类似的场板(fieldplate)结构,但工艺复杂,难与dmode工艺集成。

9、第三、成本增加,性价比下降,影响市场应用;

10、现有技术制作的均匀衬底外延片,工艺复杂性增加,工艺要求高,良率和可靠性下降,都对成本产生不利影响,在5g、wifi6、cv2x、nbiot新型通信系统等消费电子市场,成本和性价比对产品非常重要。现有技术制作的芯片的上述缺点,严重影响了市场应用。

技术实现思路

1、本发明要解决的技术问题是为了克服现有技术中的上述缺陷,提供一种半导体器件及其制备方法、电子设备。

2、本发明是通过下述技术方案来解决上述技术问题:

3、本发明的第一方面提供一种半导体器件,所述半导体器件的外延片上设有耗尽型区域和增强型区域,所述耗尽型区域为采用耗尽型工艺集成的区域,所述增强型区域为采用增强型工艺集成的区域;

4、所述外延片采用phemt结构,所述耗尽型区域和所述增强型区域的垂直结构不同,所述耗尽型区域的栅电极和所述增强型区域的栅电极的截面形状相同,均为t型。

5、可选地,所述耗尽型区域的肖特基层和所述增强型区域的肖特基层并排设置。

6、可选地,所述耗尽型区域的肖特基层和所述增强型区域的肖特基层的高度相同。

7、可选地,所述耗尽型区域中δ掺杂施主层的掺杂浓度不同于所述增强型区域中δ掺杂施主层的掺杂浓度。

8、可选地,所述耗尽型区域中隔离层的目标化学组分含量不同于所述增强型区域中隔离层的目标化学组分含量。

9、可选地,所述耗尽型区域中肖特基层的目标化学组分含量不同于所述增强型区域中肖特基层的目标化学组分含量。

10、可选地,所述半导体器件包括射频开关,位于所述耗尽型区域,所述射频开关包括发射通道和接收通道;

11、所述发射通道对应的衬底区域中δ掺杂施主层的掺杂浓度不同于所述接收通道对应的衬底区域中δ掺杂施主层的掺杂浓度;和/或,

12、所述发射通道对应的衬底区域中隔离层的目标化学组分含量不同于所述接收通道对应的衬底区域中隔离层的目标化学组分含量;和/或,

13、所述发射通道对应的衬底区域中肖特基层的目标化学组分含量不同于所述接收通道对应的衬底区域中肖特基层的目标化学组分含量。

14、可选地,所述半导体器件包括位于所述耗尽型区域的第一器件、位于所述增强型区域的第二器件以及位于所述耗尽型区域和所述增强型区域的第三器件;

15、与所述第三器件对应的耗尽型区域中隔离层的目标化学组分含量不同于与所述第一器件对应的耗尽型区域中隔离层的目标化学组分含量;和/或,

16、与所述第三器件对应的耗尽型区域中肖特基层的目标化学组分含量不同于与所述第一器件对应的增强型区域中肖特基层的目标化学组分含量;和/或,

17、与所述第三器件对应的增强型区域中δ掺杂施主层的掺杂浓度不同于与所述第二器件对应的增强型区域中δ掺杂施主层的掺杂浓度。

18、可选地,所述第一器件为射频开关或功率放大器。

19、可选地,所述第二器件为低噪声放大器。

20、可选地,所述第三器件为逻辑电路。

21、本发明的第二方面提供一种半导体器件的制备方法,所述半导体器件为第一方面所述的半导体器件;所述制备方法包括以下步骤:

22、提供衬底;

23、在所述衬底上外延生长并注入掺杂,形成所述耗尽型区域和所述增强型区域;

24、其中,在外延生长和/或注入掺杂的过程中,插入预设的掩膜版,以使阻挡的图形区域无法继续外延生长和/或无法继续注入掺杂。

25、本发明的第三方面提供一种电子设备,包括第一方面所述的半导体器件。

26、本发明的积极进步效果在于:半导体器件外延片上耗尽型区域的栅电极和增强型区域的栅电极均具有t型栅,具体可以对耗尽型区域和增强型区域的衬底进行不同的定制实现,从而提高半导体器件的性能。

27、进一步地,根据半导体器件中第一器件、第二器件以及第三器件的不同工作要求,通过对每个器件对应的衬底区域进行不同的定制,能够提高每个器件的性能,进而提高半导体器件的整体性能。

- 还没有人留言评论。精彩留言会获得点赞!