一种集成双向TVS二极管功率器件芯片的制作方法与流程

一种集成双向tvs二极管功率器件芯片的制作方法

技术领域

1.本发明涉及半导体器件制造技术领域,具体为一种集成双向tvs二极管功率器件芯片的制作方法。

背景技术:

2.传统的功率器件芯片,比如igbt、mos,门(栅)极抗电压冲击能力比较弱,几十伏的电压就可以使其击穿,导致芯片失效。tvs二极管能抑制超过其崩溃电压的过高电压,从而保护与其并联的电子器件。本发明提供了一种集成双向tvs二极管功率器件芯片的制作方法,解决了门极抗电压冲击能力弱的缺点,使功率器件芯片在封装、运输、使用过程中,得到有效保护。

技术实现要素:

3.本发明的目的在于提供一种集成双向tvs二极管功率器件芯片的制作方法,以解决上述背景技术中提出的门极抗电压冲击能力较弱的缺点问题,且流片过程中,不用增加光罩,制作简单,可靠性高。

4.为实现上述目的,本发明提供如下技术方案:一种集成双向tvs二极管功率器件芯片的制作方法,以igbt为例,包括如下步骤:s1:在n型单晶圆片蚀刻沟槽;s2:在整个芯片表面生长一层栅氧化层;s3:沉积n型多晶硅并蚀刻;s4:做p阱注入并退火;s5:做n+阱注入并退火;s6:沉积一层绝缘层;s7:芯片表面开接触孔、镀金属层做电极;s8:芯片正面栅pad开接触孔区域做p阱注入、退火,制作双向tvs二极管;s9:背面做减薄,离子注入,镀金属层作为集电极。

5.优选的,s1中,在n型单晶圆片的硅衬底的表面上形成掩膜,穿过掩膜朝向硅衬底的内部蚀刻成沟槽;掩膜为氮化硅层或二氧化硅层;对于氮化硅层为掩膜时,湿法腐蚀使用的腐蚀液为磷酸;二氧化硅层为掩膜时,所述湿法腐蚀使用的腐蚀液为氢氟酸的水溶液;所选n型单晶硅片厚度300~600μm,掺杂浓度10

13

~10

14

个/cm3;刻蚀单胞沟槽的深度5μm,直径1μm。

6.优选的,s2中,在沟槽内壁、底部及整个芯片表面生长一层栅氧化层,栅氧化层氧化温度为1000~1200摄氏度,栅氧化层的厚度为800~1000埃。

7.优选的,s3中,在沟槽内沉积n型多晶硅层,沉积温度800~1000摄氏度。沉积的n型多晶硅层作为双向tvs二极管的衬底。之后刻蚀去掉多余的多晶硅层。

8.优选的,s4中,在芯片内注入p型杂质并推结形成半导体的p阱区;离子注入能量

300~600kev,注入剂量1012~10

14

个/cm2,退火温度为950~1200摄氏度,退火时间40~60分钟。

9.优选的,s5中,对形成有p阱的衬底上进行n型杂质源注入并光刻后推结形成n+阱;离子注入能量300~600kev,注入剂量10

12

~10

14

个/cm2,退火温度为950~1200摄氏度,退火时间40~60分钟。

10.优选的,s6中,低压淀积氧化硅(lpteos)沉积:在硅片表面沉积一层绝缘层(ild)。

11.优选的,s7中,表面开接触孔、镀金属层做电极,金属层包括电镀金属层和溅射金属层。

12.优选的,s8中,在芯片正面栅pad区域开接触孔,未开孔区域作为金属掩膜,进行离子注入,并采用氟气进行退火,形成p阱区,之后制作sin钝化层。

13.优选的,s9中,在芯片背面做减薄,减薄后芯片厚度110~130μm;注入n型杂质制作场截止fs层,离子注入能量300~600kev,注入剂量10

12

~10

15

个/cm2;注入p型杂质制作p+集电极,离子注入能量50~150kev,注入剂量10

12

~10

15

个/cm2;淀积金属制作集电极,金属层材料为al/ti/ni/ag。

14.与现有技术相比,本发明的有益效果是:本发明通过在芯片流片过程中,在门极集成双向tvs二极管,双向tvs二极管可以钳制高出设定值的门极电压,从而保护门极;流片过程中,不用增加光罩,制作简单,可靠性高。

附图说明

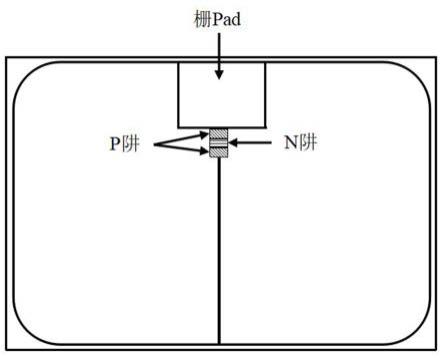

15.图1为本发明s1中沟槽示意图;图2为本发明s2中栅氧化层示意图;图3为本发明s3中多晶硅示意图;图4为本发明s4中p阱示意图;图5为本发明s5中n+阱示意图;图6为本发明s6中绝缘层示意图图7为本发明s7中金属层示意图;图8为本发明s8中双向tvs示意图;图9为本发明s9中集电极示意图;图10为本发明制作完成后,芯片电路示意图;图11为本发明工艺流程图。

具体实施方式

16.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。

17.请参阅图1-图4,本发明提供一种技术方案:一种集成双向tvs二极管功率器件芯片的制作方法,解决了门极抗电压冲击能力较弱的缺点,具有可靠性高、制作简单等优点,可用于igbt、mos等芯片的制作,本专利以igbt为例说明。

18.本发明解决其技术问题所采用的技术方案是:芯片流片过程中,在门极集成双向tvs二极管,双向tvs二极管可以钳制高出设定值的门极电压,从而保护门极。

19.包括如下步骤:s1中,在n型单晶圆片的硅衬底的表面上形成掩膜,穿过掩膜朝向硅衬底的内部蚀刻成沟槽;掩膜为氮化硅层或二氧化硅层;对于氮化硅层为掩膜时,湿法腐蚀使用的腐蚀液为磷酸;二氧化硅层为掩膜时,所述湿法腐蚀使用的腐蚀液为氢氟酸的水溶液;所选n型单晶硅片厚度300~600μm,掺杂浓度10

13

~10

14

个/cm3;刻蚀单胞沟槽的深度5μm,直径1μm。

20.s2中,在沟槽内壁、底部及整个芯片表面生长一层栅氧化层,栅氧化层氧化温度为1000~1200摄氏度,栅氧化层的厚度为800~1000埃。

21.s3中,在沟槽内沉积n型多晶硅层,沉积温度800~1000摄氏度。沉积的n型多晶硅层作为双向tvs二极管的衬底。之后刻蚀去掉多余的多晶硅层。

22.s4中,在芯片内注入p型杂质并推结形成半导体的p阱区;离子注入能量300~600kev,注入剂量1012~10

14

个/cm2,退火温度为950~1200摄氏度,退火时间40~60分钟。

23.s5中,对形成有p阱的衬底上进行n型杂质源注入并光刻后推结形成n+阱;离子注入能量300~600kev,注入剂量10

12

~10

14

个/cm2,退火温度为950~1200摄氏度,退火时间40~60分钟。

24.s6中,低压淀积氧化硅(lpteos)沉积:在硅片表面沉积一层绝缘层(ild)。

25.s7中,表面开接触孔、镀金属层做电极,金属层包括电镀金属层和溅射金属层。

26.s8中,在芯片正面栅pad区域开接触孔,未开孔区域作为金属掩膜,进行离子注入,并采用氟气进行退火,形成p阱区,之后制作sin钝化层。

27.s9中,在芯片背面做减薄,减薄后芯片厚度110~130μm;注入n型杂质制作场截止fs层,离子注入能量300~600kev,注入剂量10

12

~10

15

个/cm2;注入p型杂质制作p+集电极,离子注入能量50~150kev,注入剂量10

12

~10

15

个/cm2;淀积金属制作集电极,金属层材料为al/ti/ni/ag。

28.本发明亦适用于其它igbt,mos芯片相类似的架构。

29.本发明不局限硅类的材料,像碳化硅、氮化镓等半导体材料同样适用。

30.基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1