半导体器件及方法与流程

本发明涉及一种半导体器件。本发明还涉及一种用于制造这种半导体器件的方法。

背景技术:

1、反熔丝是一种半导体电气设备,开始时具有高电阻。在称为编程的特殊处理之后,其电阻变低,从而实现与熔丝相反的功能。反熔丝广泛用于集成电路,如可编程逻辑器件(用于设计定制)、一次性可编程只读存储器(one time programmable read-only memory,otp)中,从而修整模拟部件的值、调节电压参考电路或晶片或芯片的串行代码识别(可追溯性)。

2、在硅基技术中开发的最高效、最具成本效益的反熔丝之一是齐纳反熔丝,也称为齐纳击穿(zener zap)。它存在于双极技术、互补金属氧化物半导体(cmos)、双极cmos(bi-cmos)、混合信号和智能电源技术中。

3、齐纳器件(或一般来说称pn结或齐纳二极管)由导电类型相反的至少两个半导体元件(不同的掺杂元件)形成。一个元件是n型的,这意味着它被掺杂,使得它可以提供过量的负电荷(电子),而另一元件是p型的,并且被掺杂,使得它可以提供过量的正电荷(空穴)。

4、齐纳反熔丝通过在短时间段内向齐纳二极管施加高电压或高电流来进行编程。电压尖峰或电流尖峰导致足够的能量以使结构过热并永久损坏结构,从而使其短路。通过电流尖峰(或电压尖峰)编程称为齐纳击穿。在图1中示意性地描绘了齐纳击穿。

5、宽带隙(wide-bandgap,wbg)技术是正在开发来替代硅技术的新技术。与硅相比,它们更优的材料性能使它们更适合各种应用和领域,诸如电源应用。

6、由于包括例如以下的若干原因,齐纳反熔丝目前未用于wbg半导体技术中:

7、a)成熟度:wbg技术仍在研究和开发中,除了例如氮化镓(gan)外,还没有准备好与现有技术集成。

8、b)wbg中采用的许多拓扑是垂直的,这可能会导致难以集成器件。

9、目前,wbg技术中还没有已知的齐纳反熔丝实现。学术界和工业界最近正聚焦于在功率gan高电子迁移率晶体管(high electron mobility transistor,hemt)周围集成基本元件和电路。

10、工业界可能采用的自然解决方案可以是将gan hemt功率器件与硅基反熔丝共集成。然而,这意味着将来自两种不同技术的两个不同晶片封装在一个封装中。该解决方案可能需要复杂的封装方案,特别是在放置和布线/连接不同晶片方面。另外,可能无法确保整个共封装系统的可靠性,并且由于使用两个晶片,所得到的芯片面积可能会增加。

技术实现思路

1、本发明旨在通过在wbg技术中单片集成齐纳反熔丝来改进上述解决方案。

2、这通过独立权利要求中提供的解决方案来实现。有利的实现方式在从属权利要求中限定。

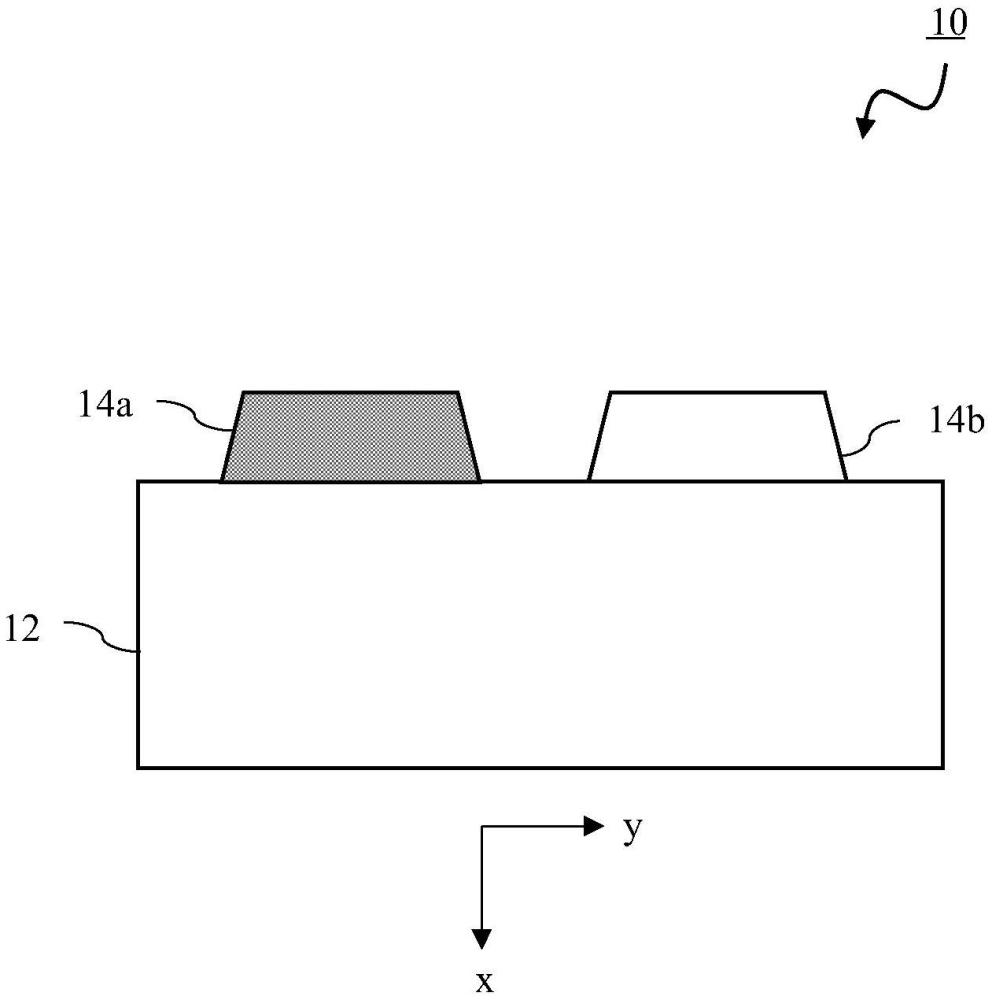

3、根据第一方面,提供了一种半导体器件,所述半导体器件包括:包括第一宽带隙半导体材料的衬底;布置在所述衬底上的第一导电类型的第一区域和第二导电类型的第二区域,其中所述第一区域和所述第二区域包括第二wbg半导体材料,并且其中所述第一区域和所述第二区域形成配置为反熔丝的齐纳pn二极管。

4、所述wbg半导体材料包括带隙在高于2ev范围内的材料。

5、根据所述第一方面,齐纳反熔丝可以单片集成在wbg技术中。

6、在所述第一方面的实现方式中,所述第一区域和所述第二区域相对于它们在所述衬底上的布置,设置为水平配置,其中所述第一区域布置在所述衬底上,并且所述第二区域布置在所述衬底上并紧邻所述第一区域。或者,所述第一区域和所述第二区域相对于它们在所述衬底上的布置,设置为垂直配置,其中所述第二区域布置在所述第一区域上,并且所述第一区域布置在所述衬底上。

7、这提供了一个优点,即齐纳反熔丝可以容易地集成在水平和垂直wbg技术中。

8、在所述第一方面的实现方式中,所述第一区域和所述第二区域间隔一定距离。或者,所述第一区域和所述第二区域是邻接的。或者,所述第一区域和所述第二区域部分重叠。

9、这提供了一个优点,即可以在时间、施加电压、施加电流和/或消耗能量方面优化编程或击穿工艺的效率。

10、在所述第一方面的实现方式中,所述第一区域具有包括第一横向突起的第一形状。所述第一横向突起具有尖端形状或截断尖端形状或另一种多边形形状,或者所述第一形状包括圆柱形形状或具有第一横向突起的圆柱形形状,其中所述第一横向突起具有尖端形状或截断尖端形状或另一种多边形形状。另外,所述第二区域具有包括第二横向突起的第二形状。所述第二横向突起具有尖端形状或截断尖端形状或另一种多边形形状,或者所述第二形状包括圆柱形形状或具有第二横向突起的圆柱形形状,其中所述横向突起具有尖端形状或截断尖端形状或另一种多边形形状。

11、这可以在时间、施加电压、施加电流和/或消耗能量方面进一步优化编程或击穿工艺的效率。

12、在所述第一方面的实现方式中,所述半导体器件还包括与所述第一区域电接触的第一金属栅极和与所述第二区域电接触的第二金属栅极。

13、这提供了一个优点,即可以在所述第一导电类型的所述第一区域和所述第二导电类型的所述第二区域之间形成金属丝,以导致电短路,并且因此实现配置为反熔丝的所述齐纳pn结的编程。

14、在所述第一方面的实现方式中,所述半导体器件还包括半导体层,所述半导体层包括第三宽带隙半导体材料。所述半导体层分别布置在所述衬底与所述第一区域和所述第二区域之间。

15、这提供了一个优点,即在所述第一区域和所述第二区域下面的区域中、在所述半导体层下方形成沟道,从而使得能够在hemt技术中实现齐纳反熔丝。

16、在所述第一方面的实现方式中,所述半导体器件还包括半导体层,所述半导体层包括第三宽带隙半导体材料,其中所述半导体层布置在所述第一区域和所述第二区域上,或者其中所述第二区域布置在所述第一区域上,并且所述半导体层布置在所述第二区域上。

17、这提供了一个优点,即在所述第一区域和所述第二区域上的区域中形成沟道,从而使得能够在垂直hemt技术中实现齐纳反熔丝。

18、在所述第一方面的实现方式中,所述第一金属栅极和所述第二金属栅极通过所述半导体层接触所述第一区域和所述第二区域。或者,所述第二金属栅极通过所述半导体层接触所述第二区域。

19、在所述第一方面的实现方式中,所述半导体器件还包括:布置在所述半导体层上的所述第一导电类型的至少一个附加第一区域和所述第二导电类型的至少一个附加第二区域,其中所述至少一个附加第一区域和所述至少一个附加第二区域包括所述第二宽带隙半导体材料;与所述至少一个附加第一区域电接触的至少一个附加第一金属栅极和与所述至少一个附加第二区域电接触的至少一个附加第二金属栅极;和至少一个附加半导体层,所述至少一个附加半导体层包括所述第三宽带隙半导体材料,并且布置在所述至少一个附加第一区域和所述至少一个附加第二区域上;其中所述至少一个附加第一金属栅极和所述至少一个附加第二金属栅极通过所述至少一个附加半导体层接触所述至少一个附加第一区域和所述至少一个附加第二区域,并且其中所述至少一个附加第一区域和所述至少一个附加第二区域形成配置为反熔丝的至少一个附加齐纳pn二极管。

20、这提供了一个优点,即可以在wbg技术中创建多堆叠齐纳反熔丝。

21、在所述第一方面的实现方式中,所述第一区域和所述第二区域布置在形成在所述衬底中的n阱结构或p阱结构中。或者,所述第一区域布置在第一阱结构中,并且所述第二区域布置在第二阱结构中,其中所述第一阱结构和所述第二阱结构包括形成在所述衬底中的n阱结构或p阱结构。

22、这提供了一个优点,即齐纳反熔丝可以集成在wbg和超宽带隙(uwbg)技术中。

23、在本发明中,uwbg半导体材料包括带隙高于4ev的半导体材料。

24、在所述第一方面的实现方式中,所述半导体器件还包括部分或完全与所述第一区域、附加地或或者与所述第二区域、附加地或或者与所述衬底接触的至少一个隔热材料结构,其中所述至少一个隔热材料结构包括二氧化硅(sio2),或包括氮化硅(si3n4)、氮化铝镓(algan)或氮化铝(aln)中的任一种的氮化合物。

25、这提供了在击穿工艺中引起热增强(例如,过热)的一个优点,这可以有助于配置为反熔丝的齐纳pn二极管的编程。

26、在所述第一方面的实现方式中,所述半导体器件还包括布置在所述第一区域与所述第二区域之间的第三导电类型的中间区域,其中所述中间区域包括所述第二宽带隙半导体材料,并且其中所述中间区域为p型区域或n型区域或未掺杂型区域。

27、这提供了进一步有助于配置为反熔丝的齐纳pn二极管的编程或击穿工艺的一个优点。

28、在所述第一方面的实现方式中,所述第二宽带隙半导体材料包括gan。

29、在所述第一方面的实现方式中,所述第三宽带隙材料包括algan。

30、在所述第一方面的实现方式中,所述第一金属栅极部分或全部与所述第一区域接触。或者,所述第一金属栅极部分或全部在所述第一区域内延伸。所述第二金属栅极部分或全部与所述第二区域接触,或者所述第二金属栅极部分或全部在所述第二区域内延伸。

31、在所述第一方面的实现方式中,所述第一金属栅极和所述第二金属栅极包括铝、钛、铜、金或其他金属元素,或包括金属堆叠,所述金属堆叠包括ni/au、ni/ag、pd/au、cr/au、pt/au、ti/pt/au、ni/si、w/si、ti/al、ti/al/ti或tin/al/tin中的任一种。

32、在所述第一方面的实现方式中,所述第一宽带隙半导体材料包括碳化硅(sic)或氧化镓(ga2o3)。或者,所述第一宽带隙半导体材料包括异质外延体材料,其中所述异质外延体材料包括氮化镓、硅(si)上gan,或sic上gan,或金刚石上gan,或绝缘体材料上宽带隙半导体。

33、根据第二方面,提供了一种用于制造半导体器件的方法。所述方法包括:提供包括第一宽带隙半导体材料的衬底;形成布置在所述衬底上的第一导电类型的第一区域和第二导电类型的第二区域,其中所述第一区域和所述第二区域包括第二宽带隙半导体材料,并且其中所述第一区域和所述第二区域形成配置为反熔丝的齐纳pn二极管。

34、所述宽带隙半导体材料包括带隙在高于2ev范围内的材料。

35、这提供了提供可以单片集成在wbg技术中的齐纳反熔丝的一个优点。

36、在所述第二方面的实现方式中,所述第一区域和所述第二区域相对于它们在所述衬底上的布置,设置为水平配置,其中所述第一区域布置在所述衬底上,并且所述第二区域布置在所述衬底上并紧邻所述第一区域。或者,所述第一区域和所述第二区域相对于它们在所述衬底上的布置,设置为垂直配置,其中所述第二区域布置在所述第一区域上,并且所述第一区域布置在所述衬底上。

37、这提供了一个优点,即齐纳反熔丝可以容易地集成在水平和垂直wbg技术中。

38、在所述第二方面的实现方式中,所述第一区域和所述第二区域间隔一定距离。或者,所述第一区域和所述第二区域是邻接的。或者,所述第一区域和所述第二区域部分重叠。

39、这提供了一个优点,即可以在时间、施加电压、施加电流和/或消耗能量方面优化编程或击穿工艺的效率。

40、在所述第二方面的实现方式中,所述第一区域具有包括第一横向突起的第一形状。所述第一横向突起具有尖端形状或截断尖端形状或另一种多边形形状,或者所述第一形状包括圆柱形形状或具有第一横向突起的圆柱形形状,其中所述第一横向突起具有尖端形状或截断尖端形状或另一种多边形形状。另外,所述第二区域具有包括第二横向突起的第二形状。所述第二横向突起具有尖端形状或截断尖端形状或另一种多边形形状,或者所述第二形状包括圆柱形形状或具有第二横向突起的圆柱形形状,其中所述横向突起具有尖端形状或截断尖端形状或另一种多边形形状。

41、这可以在时间、施加电压、施加电流和/或消耗能量方面进一步优化编程或击穿工艺的效率。

42、在所述第二方面的实现方式中,所述方法还包括形成与所述第一区域电接触的第一金属栅极和与所述第二区域电接触的第二金属栅极。

43、这提供了一个优点,即可以在所述第一导电类型的所述第一区域和所述第二导电类型的所述第二区域之间形成金属丝,以导致电短路,并且因此实现配置为反熔丝的所述齐纳pn结的编程。

44、在所述第二方面的实现方式中,所述方法还包括半导体层,所述半导体层包括分别布置在所述衬底与所述第一区域和所述第二区域之间的第三宽带隙半导体材料。

45、这提供了一个优点,即在所述第一区域和所述第二区域下面的区域中、在所述半导体层下方形成沟道,从而使得能够在hemt技术中实现齐纳反熔丝。

46、在所述第二方面的实现方式中,所述方法还包括形成包括第三宽带隙半导体材料的半导体层,其中所述半导体层布置在所述第一区域和所述第二区域上,或者其中所述第二区域布置在所述第一区域上,并且所述半导体层布置在所述第二区域上。

47、这提供了一个优点,即在所述第一区域和所述第二区域上的区域中形成沟道,从而使得能够在垂直hemt技术中实现齐纳反熔丝。

48、在所述第二方面的实现方式中,所述第一金属栅极和所述第二金属栅极通过所述半导体层接触所述第一区域和所述第二区域。或者,所述第二金属栅极通过所述半导体层接触所述第二区域。

49、在所述第二方面的实现方式中,所述方法还包括:形成布置在所述半导体层上的所述第一导电类型的至少一个附加第一区域和所述第二导电类型的至少一个附加第二区域,其中所述至少一个附加第一区域和所述至少一个附加第二区域包括所述第二宽带隙半导体材料;形成与所述至少一个附加第一区域电接触的至少一个附加第一金属栅极和与所述至少一个附加第二区域电接触的至少一个附加第二金属栅极;以及形成至少一个附加半导体层,所述至少一个附加半导体层包括所述第三宽带隙半导体材料,并且布置在所述至少一个附加第一区域和所述至少一个附加第二区域上;其中所述至少一个附加第一金属栅极和所述至少一个附加第二金属栅极通过所述至少一个附加半导体层接触所述至少一个附加第一区域和所述至少一个附加第二区域,并且其中所述至少一个附加第一区域和所述至少一个附加第二区域形成配置为反熔丝的至少一个附加齐纳pn二极管。

50、这提供了一个优点,即可以在wbg技术中创建多堆叠齐纳反熔丝。

51、在所述第二方面的实现方式中,所述第一区域和所述第二区域布置在形成在所述衬底中的n阱结构或p阱结构中。或者,所述第一区域布置在第一阱结构中,并且所述第二区域布置在第二阱结构中,其中所述第一阱结构和所述第二阱结构包括形成在所述衬底中的n阱结构或p阱结构。

52、这提供了一个优点,即齐纳反熔丝可以集成在wbg和uwbg技术中。

53、在本发明中,uwbg半导体材料包括带隙高于4ev的半导体材料。

54、在所述第二方面的实现方式中,所述方法还包括形成部分或完全与所述第一区域、附加地或或者与所述第二区域、附加地或或者与所述衬底接触的至少一个隔热材料结构,其中所述至少一个隔热材料结构包括sio2,或包括si3n4、algan或aln中的任一种的氮化合物。

55、这提供了在击穿工艺中引起热增强(例如,过热)的一个优点,这可以有助于配置为反熔丝的齐纳pn二极管的编程。

56、在所述第二方面的实现方式中,所述方法还包括形成布置在所述第一区域与所述第二区域之间的第三导电类型的中间区域,其中所述中间区域包括所述第二宽带隙半导体材料,并且其中所述中间区域为p型区域或n型区域或未掺杂型区域。

57、这提供了进一步有助于配置为反熔丝的齐纳pn二极管的编程或击穿工艺的一个优点。

58、在所述第二方面的实现方式中,所述第二宽带隙半导体材料包括gan。

59、在所述第二方面的实现方式中,所述第三宽带隙材料包括algan。

60、在所述第二方面的实现方式中,所述第一金属栅极部分或全部与所述第一区域接触。或者,所述第一金属栅极部分或全部在所述第一区域内延伸。所述第二金属栅极部分或全部与所述第二区域接触,或者所述第二金属栅极部分或全部在所述第二区域内延伸。

61、在所述第一方面的实现方式中,所述第一金属栅极和所述第二金属栅极包括铝、钛、铜、金或其他金属元素,或包括金属堆叠,所述金属堆叠包括ni/au、ni/ag、pd/au、cr/au、pt/au、ti/pt/au、ni/si、w/si、ti/al、ti/al/ti或tin/al/tin中的任一种。

62、在所述第二方面的实现方式中,所述第一宽带隙半导体材料包括sic或ga2o3。或者,所述第一宽带隙半导体材料包括异质外延体材料,其中所述异质外延体材料包括si上gan,或sic上gan,或金刚石上gan,或绝缘体材料上宽带隙半导体。

63、根据所述第二方面及其实现方式所述的方法提供了与如上文针对所述第一方面及其相应实现方式的所述器件所述的相同的优点和效果。

- 还没有人留言评论。精彩留言会获得点赞!