非易失性存储芯片及其漏电流补偿电路的制作方法

本公开涉及芯片,尤其涉及一种非易失性存储芯片及其漏电流补偿电路。

背景技术:

1、slc(单层单元存储技术)nor flash(一种非易失性闪存技术)芯片常用来作为代码存储,一个独立的存储阵列是由多个wl(字线)(比如256字线或者512字线甚至1024字线)和多个bl(位线)(比如2048位线或者4096位线甚至8192位线)组成,图1为现有技术中一示例性的非易失性存储芯片的存储阵列的结构示意图,图1所示是一个由1024字线和8192位线组成的nor flash存储阵列示意图。阵列之外设计者会设计一个可以进行阈值调整的参考cell(单元),给存储阵列提供读操作的参考电流,当然也有设计者会直接从基准电流源产生一个参考电流。读操作各个端口的偏置条件如下:csl(common source line,公共源极线)偏置在0v(伏特),选中的字线偏置在vread(一个电压值),未选中的位线偏置在0v,选中的位线偏置在vbl(0.7到1v)。根据存储的数据的不同,位线上的电流也不一样,这个电流会与参考电流通过灵敏放大器进行比较进而判断出选中的cell所存储的数据值是0还是1。

2、在图1的阵列里每一根位线上并联着1024个cell,这意味着除了选中的cell会提供位电流之外,未选中的1023个cell也会贡献漏电流。长沟道的nor flash芯片设计会忽略读操作未选中cell的漏电流的影响,原因有两个:1)长沟道的nor flash工艺沟道长度足够长,栅极氧化层足够厚,无论是沟道漏电流还是gidl(gate-induced drain leakage,栅诱导漏极泄漏电流)都比较小;2)擦除算法会把over erase cell(过擦除单元)的阈值拉高,从而在读操作时未选中cell的漏电流影响较小。但是随着沟道长度越来越小,栅极氧化层厚度越来越薄,沟道漏电流和gidl电流会影响到读出的数据,因此未选中cell的漏电流对读操作的影响就显现出来了。

3、传统的nor flash芯片设计一般会在未选中字线上施加负压来抑制擦除校验时over erase cell的沟道漏电流,但是施加的负压在减小了沟道漏电流的同时也会增加gidl漏电流,并且阈值电压越高,栅极电压越负,gidl漏电流也越大,这会影响到擦除校验的精度,因此在擦除校验中对漏电流进行补偿也是很有必要的。

4、现有的漏电流补偿更加关注global bitline(全局位线)的ac(交流)电流的补偿,而对未选中cell的漏电流一般采用抑制的方案,具体实施如下:在未选中字线上施加负压来抑制沟道漏电流,而抑制漏电流的方案缺陷有两个:1)施加的负压在减小了沟道漏电流的同时会增加gidl漏电流,并且阈值电压越高,栅极电压越负,gidl漏电流也越大,此消彼长,抑制的效果就会减弱;2)负电压的建立需要一定的时间,对于擦除校验或者过擦除校验这个建立时间是可以接受的,但是对于读操作这个建立时间是不能接受的,而如果一直维持负压就会导致standby(待机)电流增大,不适用于低功耗应用。

技术实现思路

1、本公开要解决的技术问题是为了克服现有技术中在对非易失性存储芯片读操作过程中,无法对未选中cell的漏电流进行及时、有效且可靠的补偿,导致非易失性存储芯片的可靠性降低的缺陷,提供一种非易失性存储芯片及其漏电流补偿电路。

2、本公开是通过下述技术方案来解决上述技术问题:

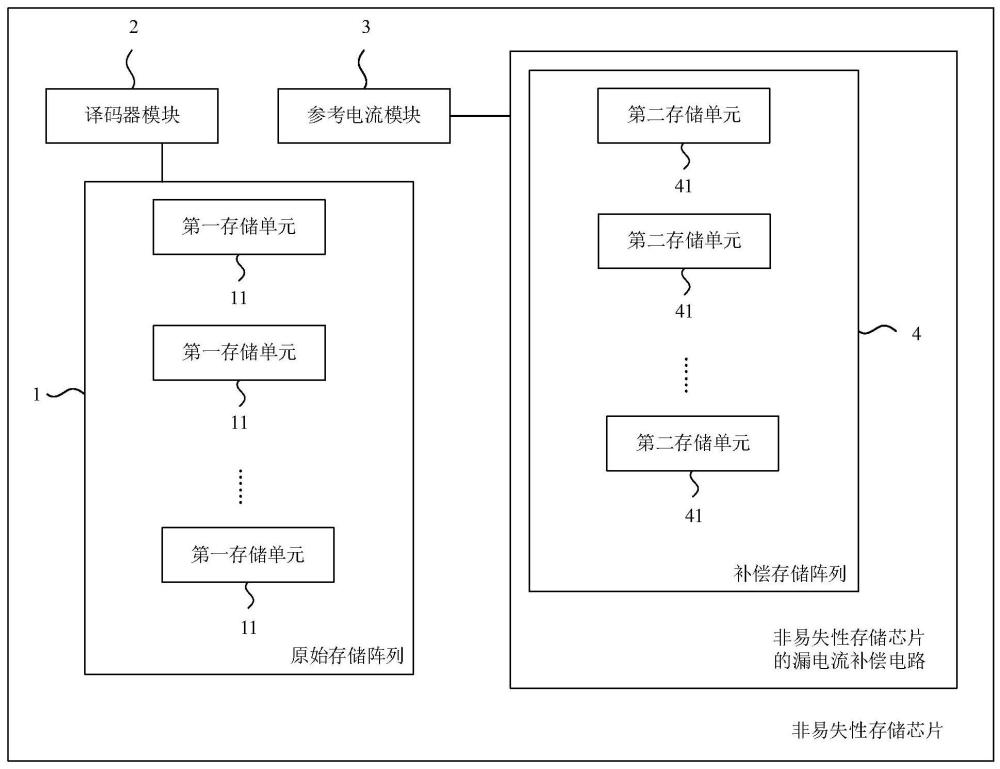

3、第一方面,提供一种非易失性存储芯片的漏电流补偿电路,所述非易失性存储芯片包括原始存储阵列、译码器模块和参考电流模块;

4、所述原始存储阵列包括若干个第一存储单元;

5、所述参考电流模块用于为所述原始存储阵列提供读操作对应的参考电流;

6、所述译码器模块用于在若干个所述第一存储单元中选中用于读操作的目标存储单元;

7、所述漏电流补偿电路包括补偿存储阵列,所述补偿存储阵列包括若干个第二存储单元;

8、其中,所述第二存储单元的数量和规格参数基于所述第一存储单元的数量和规格参数确定;

9、所述漏电流补偿电路用于在对所述目标存储单元执行读操作时,对所述目标存储单元所处位线上的第一漏电流进行补偿。

10、本公开的漏电流补偿电路中补偿存储阵列的第二存储单元的数量和规格参数,基于原始存储阵列中第一存储单元的数量和规格参数确定,使得补偿电流的温度特性与原始array cell的真实漏电流相适配,无论高低温操作时,都能达到相适配的补偿效果,补偿效果不受工艺和温度的影响。在对非易失性存储芯片的原始存储阵列中的目标存储单元执行读操作时,可以通过漏电流补偿电路对目标存储单元所处位线上的第一漏电流进行补偿;漏电流补偿电路结构简单且易于实现,能够及时、有效且可靠的对未选中cell的漏电流进行补偿,提高了非易失性存储芯片的可靠性。

11、较佳地,所述原始存储阵列包括nw条第一字线、nb条第一位线和nw*nb个所述第一存储单元,每条所述第一位线并联有nw个所述第一存储单元,每条所述第一字线并联有nb个所述第一存储单元,nw和nb均为正整数;

12、所述补偿存储阵列包括mw条第二字线和mb条第二位线,mw条所述第二字线相连接且mb条所述第二位线相连接,所述第二位线并联有mw*mb个所述第二存储单元,mw和mb均为正整数;

13、其中,mw*mb=nw。

14、本公开的非易失性存储芯片的漏电流补偿电路,基于非易失性存储芯片中原始存储阵列,设计出独特的、与原始存储阵对应的补偿存储阵列,在对原始存储阵列中的目标存储单元执行读操作时,可以通过漏电流补偿电路中的补偿存储阵列对目标存储单元所处位线上的第一漏电流进行补偿;补偿存储阵列结构紧凑、面积较小,且能够及时、有效且可靠的对未选中cell的漏电流进行补偿,补偿效果不受工艺和温度的影响,提高了非易失性存储芯片的可靠性。

15、较佳地,所述原始存储阵列包括1024条所述第一字线、8192条所述第一位线和1024*8192个所述第一存储单元;

16、所述补偿存储阵列包括32条所述第二字线、32条所述第二位线和1024个所述第二存储单元。

17、较佳地,所述补偿存储阵列中的第二存储单元的规格参数,与所述原始存储阵列中的第一存储单元的规格参数相同。

18、本公开的非易失性存储芯片的漏电流补偿电路,补偿存储阵列中的第二存储单元的规格参数,与原始存储阵列中的第一存储单元的规格参数相同,使得补偿电流的温度特性与原始array cell的真实漏电流完全适配,无论高低温操作时,都能达到相适配的补偿效果,补偿效果不受工艺和温度的影响。在对非易失性存储芯片的原始存储阵列中的目标存储单元执行读操作时,可以通过漏电流补偿电路对目标存储单元所处位线上的第一漏电流进行补偿;漏电流补偿电路结构简单且易于实现,能够及时、有效且可靠的对未选中cell的漏电流进行补偿,提高了非易失性存储芯片的可靠性。

19、较佳地,所述补偿存储阵列中的所述第二存储单元对应本征状态。

20、本公开的非易失性存储芯片的漏电流补偿电路,可以通过补偿存储阵列对目标存储单元所处位线上的第一漏电流进行补偿;补偿存储阵列中的第二存储单元对应本征状态,本征状态的漏电流补偿是一种对全1背景数据和全0背景数据漏电流补偿的一种折中选择,无需特意区分读操作对应的数据值,均能实现对第一漏电流的补偿;补偿存储阵列结构紧凑、面积较小,且能够及时、有效且可靠的对未选中cell的漏电流进行补偿,补偿效果不受工艺和温度的影响,提高了非易失性存储芯片的可靠性。

21、较佳地,所述译码器模块包括字线译码器和位线译码器;

22、所述字线译码器用于接收第一读字线电压,确定读操作对应的目标字线;

23、所述位线译码器用于接收第一读位线电压,确定读操作对应的目标位线,以选中所述目标存储单元。

24、较佳地,所述漏电流补偿电路还应用于对所述非易失性存储芯片的校验操作;

25、所述校验操作包括擦除校验操作,和/或过擦除校验操作,和/或编程校验操作。

26、较佳地,所述补偿存储阵列的所述第二字线用于在校验操作时接收第二读字线电压;

27、所述第二读字线电压与所述第一读字线电压相等。

28、较佳地,所述非易失性存储芯片还包括放大器;

29、对所述目标存储单元执行读操作时,所述放大器的第一输入端用于接收所述第一漏电流,及所述目标存储单元对应的位电流,并基于所述第一漏电流和所述位电流之和得到第一电流;

30、所述放大器的第二输入端用于接收所述参考电流,及所述补偿存储阵列对应的第二漏电流,并基于所述参考电流和所述第二漏电流之和得到第二电流;

31、所述放大器的输出端用于在所述第一电流大于所述第二电流时,确定所述目标存储单元存储的数据值为1;

32、所述放大器的输出端用于在所述第一电流小于所述第二电流时,确定所述目标存储单元存储的数据值为0。

33、第二方面,还提供一种非易失性存储芯片,所述非易失性存储芯片包括原始存储阵列、译码器模块和参考电流模块,以及上述的非易失性存储芯片的漏电流补偿电路。

34、在符合本领域常识的基础上,上述各优选条件,可任意组合,即得本公开各较佳实例。

35、本公开的积极进步效果在于:

36、本公开的非易失性存储芯片及其漏电流补偿电路,漏电流补偿电路中第二存储单元的数量和规格参数基于第一存储单元的数量和规格参数确定,使得补偿电流的温度特性与原始array cell的真实漏电流相适配,无论高低温操作时,都能达到相适配的补偿效果,补偿效果不受工艺和温度的影响。在对非易失性存储芯片的原始存储阵列中的目标存储单元执行读操作时,可以通过漏电流补偿电路对目标存储单元所处位线上的第一漏电流进行补偿;漏电流补偿电路结构简单且易于实现,能够及时、有效且可靠的对未选中cell的漏电流进行补偿,提高了非易失性存储芯片的可靠性。

- 还没有人留言评论。精彩留言会获得点赞!